Fragt man heutige Anwender von IBM i, wie viele „Cores“ sie für ihre „Kernanwendung“ benötigen, kommen meist ernüchternde Antworten: Ein Core reicht, manchmal zwei, in wenigen Fällen deren vier. Doch beim künftigen Power10-Prozessor arbeiten bis zu 15 Cores in einer CPU. Daher lautet eine wichtige Frage für bestehende Anwender, wie stark die Rechenleistung in einem einzigen Core der kommenden Generation steigen wird.

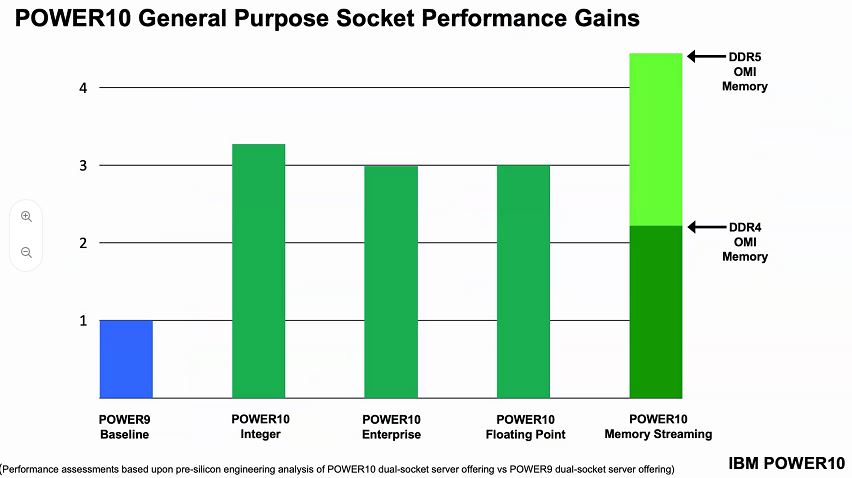

Beim Power9-Prozessor sind bis zu 12 Cores aktiv, beim Power10 sind 16 vorgesehen, von denen jedoch nur 15 aktiviert werden. Das soll die Ausbeute des Fertigungsprozesses (immerhin auf einer 7-nm-Fabrikationslinie, Hersteller Samsung) verbessern. IBM hat allerdings beim Design des neuen Bausteins die einzelnen Cores komplett neugestaltet. Daher soll, so die Ausführungen auf der Hot Chip-Konferenz, die reine Integer-Performance um den Faktor 3 bei „Enterprise Workloads“ gegenüber der Vorgängergeneration ansteigen. Dabei bleibt die Taktfrequenz für die Bausteine der kommenden Generation bei 4 GHz.

Wer nicht mehrere Anwendungen auf seiner „nächsten IBM i“ konsolidieren möchte und nach wie vor mit einem Core gut bedient ist, der sollte nachdenken, ob er seine Anwendungen nicht in eine „Power Cloud“ migriert. Die ersten Systeme auf der Basis von Power 10 sind für 2021 geplant, also 30 Jahre nach Gründung des PowerPC Konsortiums. Auch nach der Publikation der wichtigsten Spezifikationen dieses Chips bleibt Raum für Spekulationen, was von den zukünftigen Systemen zu erwarten ist.

Power9 als aktuelle Generation

Nichtsdestotrotz erneuerte IBM in diesem Jahr seine auf dem Power9-Chip basierende Systemfamilie und bietet mittlerweile im Scale-out-Umfeld die sogenannten G-Modelle an. Am eigentlichen Systemdesign wurde zwar nichts grundlegend geändert, aber mit neuen Boards und neuen Adaptern treibt IBM die Nutzung von „PCI Gen4“ und den Einsatz der NVMe-Technik voran, um so Datentransfers weiter zu beschleunigen.

Zudem wurden mit der „Power Private Cloud With Dynamic Capacity“ die bereits im Enterprise-Sektor existierenden „Pay-per-use“-Bezahlmodelle verbessert und auf Zweisockel-Power-Systeme ausgeweitet. So werden Prozessoren, bei Enterprise Modellen auch Memory, von mehreren Systemen als ein gemeinsamer Ressourcen Pool betrachtet. Davon profitieren die Anwender, sind sie doch in der Lage, individuell zu entscheiden, wieviel dieser Ressourcen sie dauerhaft nutzen möchten. Darüber hinaus benötigte Pool Ressourcen werden über „Pre-paid Credits“ abgerechnet. Darunter versteht sich folgendes Abrechnungsmodell: Wenn die Ressourcennutzung, die aggregierten Basisressourcen des Pools überschreitet, wird minütlich die gemessene Kapazität für die Kostenberechnung herangezogen und in Echtzeit mit dem gekauften Kapazitätsguthaben verrechnet.

Das Power Cloud Offering der IBM wird ebenfalls kontinuierlich weiterentwickelt. SAP HANA ist für die Nutzung in der Power Cloud zertifiziert und steht nun auch als Power Virtual Server in der IBM-Cloud zur Verfügung. Um Netzwerkkosten zu senken, gibt es seit diesem Jahr für die Verbindung von IBMs „Classic x86-Cloud“ zur Power-Kollokation einen kostenfreien, redundanten 5GBit/s „DirectLink“. Die Kombination aus Power Virtual Server zusammen mit dem „Power Private Cloud“-Angebot ermöglicht den Zugriff auf kosteneffiziente Hybrid-Cloud-Architekturen für die Nutzung der IBM Power Technologie.

Kommende Systemgenerationen

30 Jahre nach Gründung des PowerPC-Konsortiums, wird IBM die ersten Power10-basierten Server im Markt einführen – und somit die zehnte CPU-Generation verwenden. Die einfache Rechnung dazu lautet, dass im Schnitt alle drei Jahre eine neue Chip-Generation zum Einsatz gebracht wird. Demzufolge verspricht die aktuelle IBM Power Roadmap, dass bereits 2021/2022 die Power10-Systeme die heutigen Modelle ablösen. Den Chip wird es, wie bereits bei Power9, in SMT8- und SMT4-Varianten geben. Die maximale Anzahl von Kernen (je nach SMT-Version) wird mit 15 bzw. 30 angeben, so dass 120 Threads pro Chip gleichzeitig verarbeitet werden können.

Im Unterschied zu Power9 soll es auch Dual-Chip-Module geben, was letztendlich zu maximal 240 Threads pro Sockel führt. Das sind zweieinhalbmal mehr Threads pro Sockel als bei aktuellen Systemen. Erste Analysen gehen von einer Verdreifachung der Performance pro Sockel aus. Dabei soll der Chip insgesamt wesentlich Energie-sparender arbeiten, als sein Vorgänger.

Das Open Memory Interface mit einer Bandbreite von bis zu 1 TByte/s ermöglicht die Verwendung von DDR4, DDR5 als auch GDDR DIMMs. Obwohl ein PowerAXON Interface bereits im Power9-Chip vorhanden war, wird es erst mit seiner Weiterentwicklung in Power10 Anwendung finden. Letztendlich wird dadurch ermöglicht, dass ein System den Hauptspeicher anderer Knoten des gleichen Clusters bei Bedarf nutzen kann. Die Zugriffsgeschwindigkeit nimmt dabei zwar ab, ist ausreichend für „relaxed latency“ Workload. Die Skalierbarkeit wird dabei mit maximal 2 PByte pro Cluster angegeben.

Diese sogenannten „Memory Inception“ Fähigkeiten sind ein Schritt in Richtung „Composable Datacenter“, also einem riesigen Pool von Ressourcen, die mittels Software orchestriert logischen Servern zugeordnet werden, um genau das zur Verfügung zu haben, was für die jeweilige Arbeitslast benötigt wird. (rhh)